- Revised: 23-Sep-2000, J. Zbiciak

- Reverse Engineered by Joe Zbiciak and Frank Palazzolo.

## Introduction

The SP-0256 Speech Processor is an extension to the General Instruments SP-0250 speech processor. The SP-0250 Speech Processor is a 12-pole IIR filter / LPC-based speech generator. It is constructed from a single two-pole filter stage and some control circuitry that multiplexes filter coefficients and samples to achieve a 12-pole filter. It provides a pitch and noise generator for exciting the filter, thus providing all of the necessary equipment for LPC-based speech synthesis.

The original SP-0250 was suitable for generating synthetic voice, but it requires significant attention from the host microprocessor as it consumed speech data. Also, the speech data itself tended to occupy quite a bit of space. The SP-0256 addresses these issues by adding a small microsequencer to the device which is responsible for updating speech core's LPC coefficients. It additionally provides a rudimentary but effective form of compression, as words and phrases could be constructed from small subroutines, and individual filter updates could be restricted to a subset of the total parameter set, encoding only the significant bits.

## Architecture

The SP-0256 consists of the following elements:

- A digital filter core, containing:

- A periodic impulse and white-noise generator,

- A 12-pole IIR filter,

- Twelve 8-bit filter coefficient registers,

- One 6-bit repeat register,

- One 8-bit pitch register,

- One 8-bit amplitude register,

- Two 8-bit interpolation registers, one for pitch, one for amplitude, and

- One 8-bit to 10-bit translation ROM for expanding filter coefficients. (This ROM is not accessible from the sequencer.)

- A small microsequencer, containing:

- One 16-bit program counter,

- A single-level program stack,

- An 8-bit "command address" register,

- A 2-bit MODE register,

- A 2-bit repeat prefix,

- Control logic for interpreting an instruction stream.

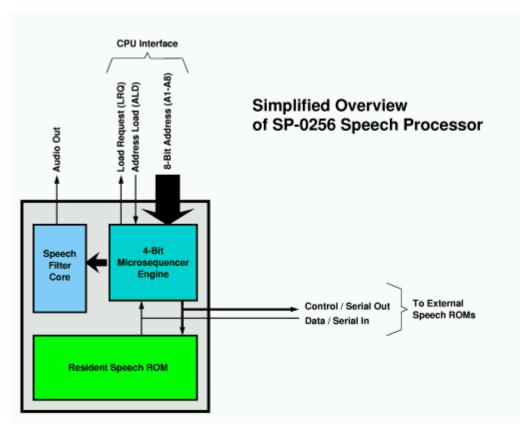

This diagram gives a rough overview of the SP-0256's architecture:

The digital filter contains all of the pieces necessary to generate the actual speech sounds. The impulse generator and IIR filter model the vocal tract by shaping the periodic impulses in a similar manner to how the human vocal tract shapes sound. This core operates largely independently of the microsequencer, except that it relies on the microsequencer to receive parameter updates, and it notifies the microsequencer when it completes an utterance.

The microsequencer is a simple machine which focuses soley on copying parameters from its input to the filter parameter registers in the filter core. It can zero, replace or delta-update the existing values of the filter registers. It is also capable of branching and jumping to subroutines. The sequencer is not Turing complete, in that it is not capable of conditional flow.

In order to control the filter core, the microsequencer can address 17 different registers in the filter core. Those registers are:

| Register                   | Size   | Purpose                                                                                                                                                       |

|----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Repeat                     | 6 bits | Repeat counter                                                                                                                                                |

| Pitch                      | 8 bits | Pitch period. A period of 0 generates white noise for <i>unvoiced</i> sounds.                                                                                 |

| Amplitude                  | 8 bits | Speech amplitude, in floating-point format. It is divided into two fields the 3 MSBs provide the <i>exponent</i> and the 5 LSBs provide the <i>mantissa</i> . |

| BØ                         | 8 bits |                                                                                                                                                               |

| FØ                         | 8 bits |                                                                                                                                                               |

| B1                         | 8 bits |                                                                                                                                                               |

| F1                         | 8 bits |                                                                                                                                                               |

| B2                         | 8 bits |                                                                                                                                                               |

| F2                         | 8 bits | Filter coefficients                                                                                                                                           |

| В3                         | 8 bits |                                                                                                                                                               |

| F3                         | 8 bits |                                                                                                                                                               |

| B4                         | 8 bits |                                                                                                                                                               |

| F4                         | 8 bits |                                                                                                                                                               |

| В5                         | 8 bits |                                                                                                                                                               |

| F5                         | 8 bits |                                                                                                                                                               |

| Pitch<br>Interpolation     | 8 bits | Delta update value applied to pitch after each period.                                                                                                        |

| Amplitude<br>Interpolation | 8 bits | Delta update value applied to amplitude after each period.                                                                                                    |

Additionally, the microsequencer has a couple registers of its own. These registers primarily control how the microsequencer behaves.

| Register         | Size   | Purpose                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE             | 2 bits | Controls the format of data which follows various instructions. In some cases, it also controls whether certain filter coefficients are zeroed or left unmodified. The exact meaning of MODE varies by instruction. MODE is <i>sticky</i> , meaning that once it is set, it retains its value until it is explicitly changed by Opcode <u>1000</u> (SETMODE) or the sequencer halts. |

| REPEAT<br>PREFIX | 2 bits | The parameter load instructions can provide a four bit repeat value to the filter core. This register optionally extends that four bit value by providing two more significant bits in the 2 MSBs. By setting the repeat prefix with Opcode $1000$ (SETMODE), the program can specify repeat values up to \$3F (63). This register is <i>not</i> sticky.                             |

| PAGE             | 4 bits | The PAGE register acts as a prefix, providing the upper four address bits for every <u>JMP</u> and <u>JSR</u> instruction. The PAGE                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | register can hold any binary value from 0001 to 1111, and is set by the <u>SETPAGE</u> instruction. It is not possible to load it with 0000. It powers up to the value 0001, and it retains its value across JMP/JSR instructions as well as sequencer halts.                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC       16 bits       the program counter is kept in every Speech ROM that is attached to the SP0256, so that the program counter is broadcast on JMP or JSR.         STACK       16 bits       This is where the program counter is saved when performing a JSR. The STACK has room for exactly one a nested subroutines are not possible. It holds the address of the <i>byte</i> following the JSR instruction.         COMMAND       8 bits       This node address of the most recent command from the host CPU. Addresses are loaded into this register. When a new command address is available, it copies these bits to bits 1 through 8 |  | This is the program counter. This counter tracks the address of the <i>byte</i> that is currently being processed. A copy of the program counter is kept in every Speech ROM that is attached to the SP0256, so that the program counter is only broadcast on <u>JMP</u> or <u>JSR</u> .                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | This is where the program counter is saved when performing a <u>JSR</u> . The STACK has room for exactly one address, so nested subroutines are not possible. It holds the address of the <i>byte</i> following the JSR instruction.                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | This holds address of the most recent command from the host CPU. Addresses are loaded into this register via external pins and the ALD control line. When the microsequencer is halted (or is about to halt), it watches for an address in this register. When a new command address is available, it copies these bits to bits 1 through 8 of the program counter. Bits 0, 9 through 11, and 13 through 15 are forced to zero. Bit 12 is forced to 1 so that code executes out of page \$1. |

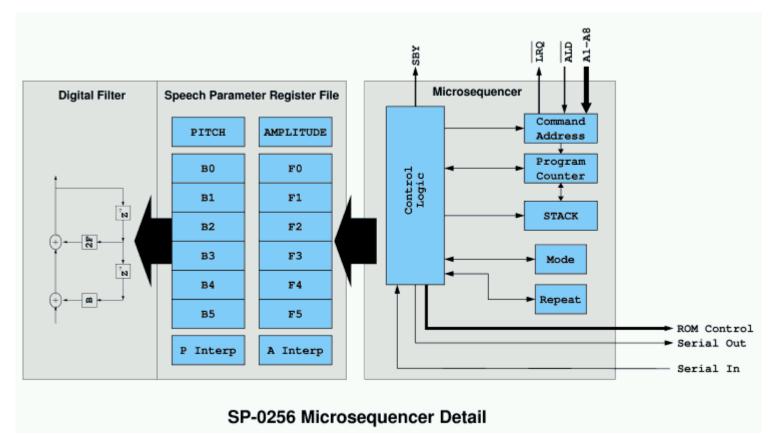

This diagram gives a conceptual overview of how the microsequencer interfaces to the rest of the machine.

# **General Notes Regarding the SP-0256 Instruction Set**

The microsequencer's instruction set can be divided into three primary categories:

- Speech parameter updates (replacement or delta-update),

- Control transfer (<u>JMP</u>, <u>JSR</u> and <u>RTS</u>), and

- Microsequencer mode/state updates (<u>SETMODE</u> and <u>SETPAGE</u>).

Speech parameter updates are generally followed by a data block whose format depends on the particular instruction issued. Most of these instructions only update a subset of the total speech parameter set, and often they update only the most significant bits of the registers they modify. The data blocks themselves are a variable number of bits, and are *not* constrained to byte boundaries.

The instruction stream itself is processed as a sequence of bits, not bytes, and so instructions and their data blocks can start on any bit boundary. Ordinarily, there are no gaps between instructions, and so the machine largely behaves as a bit-aligned machine. Control transfer instructions introduce *alignment points*, as all addresses in the system are byte addresses, and so all branch targets (including the return-branch target for <u>RTS</u>) are on byte boundaries. It is customary to pad the data stream with 0s at alignment points (eg. after <u>JSR</u> instructions).

The instruction reference below shows the exact data formats that each instruction requires. Note that the data format for an instruction varies according to the current MODE setting, and so the machine provides a large variety of data formats.

Other important things to note are:

- On instructions that accept a repeat count, a repeat count of zero causes the instruction to not execute, which means that *no data block follows the instruction* in that case. (My disassembler currently does not handle this case.) (This part may be in error. Conflicting documentation suggests there's more going on here than we worked out.)

- As a matter of convention in this document, bits are packed into bytes left-to-right, with the leftmost bit going in the MSB of the first byte, and the LSB of the first byte being logically adjacent to the MSB of the second byte. This is likely backwards from how the hardware looks at it, but it is the most natural for a human interpreting the data, as it reads from left-to-right.

- Most bit fields, except those which specify branch targets, are bit reversed, meaning the left-most bit is the LSB.

- Bit fields narrower than 8 bits are *MSB justified* unless specified otherwise, meaning that the least significant bits are the ones that are missing. These LSBs are filled with zeros.

- When updating filter coefficients with a delta-update, the microsequencer performs plain 2s-complement arithmetic on the 8-bit value in the coefficient register file. No attention is paid to the format of the register.

### Key for opcode formats below

9/12/2017 ....

SP0256 Instruction Set

| Field     | Description                                                                                                                                                                                                                                                  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ААААААА   | Amplitude bits. The 3 rightmost bits are the exponent. The exponent determines what power of 2 is applied to the lower 5 bits.                                                                                                                               |  |

| РРРРРРР   | Pitch period. When set to 0, the impulse switches to random noise. For timing purposes, noise and silence have an effective period equivalent to period==64.                                                                                                 |  |

| BBBBBBBS  | B coefficient data. The 'S' is the sign bit, if present. If there is no 'S' on a given field, the sign is assumed to be 0.                                                                                                                                   |  |

| FFFFFFS   | F coefficient data.                                                                                                                                                                                                                                          |  |

| RRRR      | Repeat bits. On Opcode <u>1000</u> (SETMODE), the repeat bits go to the two MSBs of the repeat count for the <i>next</i> instruction. On all other instructions, the repeat bits go to the four LSBs of the repeat count for the <i>current</i> instruction. |  |

| ММ        | Mode bits. These are set by Opcode <u>1000</u> (SETMODE), and they control the data format for a number of other instructions.                                                                                                                               |  |

| LLLLLLL   | Byte address for a branch target. Branch targets are 16 bits long. The JMP/JSR instruction provides the lower 12 bits, and the PAGE register provides the upper 4 bits. The PAGE register is modified via the SETPAGE instruction, Opcode <u>0000</u> .      |  |

| ааааа     | Amplitude delta. (unsigned)                                                                                                                                                                                                                                  |  |

| ррррр     | Pitch delta. (unsigned)                                                                                                                                                                                                                                      |  |

| aaas      | Amplitude delta. (2s complement)                                                                                                                                                                                                                             |  |

| ppps      | Pitch delta. (2s complement)                                                                                                                                                                                                                                 |  |

| bbbs fffs | Filter coefficient deltas. (2s complement)                                                                                                                                                                                                                   |  |

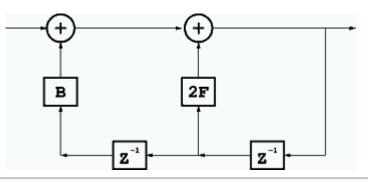

For reference, each 2nd order filter section looks like so. Note that "1/Z" represents a single unit delay. Altogether, there are 6 such stages, yielding a 12 pole filter. The exact ordering of the stages with respect to the coefficient data formats appears to be straightforward, with the lowest-numbered coefficient pair used in the earliest filter stage, etc.

# **Instruction Set Quick Reference**

| Opcode  | Mnemonic        | Description                                                                |

|---------|-----------------|----------------------------------------------------------------------------|

| 0000    | RTS/SETPAGE     | Return OR set the PAGE register                                            |

| 0001    | LOADALL         | Load All Parameters                                                        |

| 0010    | LOAD_2          | Load Pitch, Amplitude, Coefficient, and Interpolation Regsisters           |

| 0011    | <u>SETMSB_3</u> | Load Pitch, Amplitude, MSBs of 3 Coefficients, and Interpolation Registers |

| 0100    | LOAD_4          | Load Pitch, Amplitude, Coefficients (2 or 3 stages)                        |

| 0101    | <u>SETMSB_5</u> | Load Pitch, Amplitude, and MSBs of 3 Coefficients                          |

| 0110    | <u>SETMSB_6</u> | Load Amplitude and MSBs of 2 or 3 Coefficients                             |

| 0111    | <u>JMP</u>      | Jump to 12-bit PAGE-relative Address                                       |

| 1000    | <u>SETMODE</u>  | Set the Mode bits and Repeat MSBs                                          |

| 1001    | DELTA_9         | Delta update Amplitude, Pitch and 5 or 6 Coefficients                      |

| 1010    | <u>SETMSB_A</u> | Load Amplitude and MSBs of 3 Coefficients                                  |

| 1011    | <u>JSR</u>      | Jump to Subroutine (12-bit PAGE-Relative Address)                          |

| 1 1 0 0 | LOAD_C          | Load Pitch, Amplitude, Coefficients (5 or 6 stages)                        |

| 1 1 0 1 | DELTA_D         | Delta update Amplitude, Pitch and 2 or 3 Coefficients                      |

| 1 1 1 0 | LOAD_E          | Load Pitch, Amplitude                                                      |

| 1111    | PAUSE           | Silent pause                                                               |

# **Individual Instruction Descriptions**

| [ <u>Ref</u> ] [ <u>Top</u> ] |                                                                                                            |                                 |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| OPCODE<br>0000                | RTS / SETPAGE                                                                                              | Return or set the PAGE register |  |

| Format                        | LLLL 0000                                                                                                  |                                 |  |

| Action                        | It slices, it dices, it juliennes! It's a floor wax! It's a dessert topping! It's two instructions in one! |                                 |  |

|                               |                                                                                                            |                                 |  |

### • SETPAGE

When LLLL is non-zero, this instruction sets the PAGE register to the value in LLLL. The PAGE register determines which 4K page (eg. the upper four bits of the address for) the next JMP or JSR will jump to. (Note that address loads via ALD appear to ignore PAGE, and set the four MSBs to \$1000. They do not modify the PAGE register, so subsequent JMP/JSR instructions will jump relative to the current value in PAGE.)

The PAGE register retains its setting until the next SETPAGE is encountered. Valid values for PAGE are in the range \$1...\$F. The RESROM starts at address \$1000, and no code exists below that address. Therefore, the microsequencer can address speech data over the address range \$1000 through \$FFFF, for a total of 60K of speech data. (Up to 64K may be possible by jumping to a location near \$FFFF and letting the address wrap around. At this time, the exact behavior of an address wraparound is unknown, and may be dependent on the behavior of both the microsequencer *and* the attached speech ROMs.)

### • RTS

When LLLL is zero, this opcode causes the microsequencer to pop the PC stack into the PC, and resume execution there. The contents of the stack are replaced with \$0000 (or some other flag which represents an *empty stack*). If the address that was popped was itself \$0000 (eg. an *empty stack*), execution **halts**, pending a new address write via ALD. (Of course, if an address was previously written via ALD and is pending, control transfers to that address immediately.)

| [ <u>Ref</u> ] [ <u>Top</u> ] |                  |                                                                                                                                                                                                                                    |  |

|-------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OPCODE<br>0001                | LOADALL          | Load All Parameters                                                                                                                                                                                                                |  |

| Format                        | RRRR 0001 [data] |                                                                                                                                                                                                                                    |  |

| Data<br>Formats,<br>by MODE   |                  | AAAAAAAA PPPPPPPP<br>BBBBBBS FFFFFFS (coeff pair 0)<br>BBBBBBBS FFFFFFS (coeff pair 1)<br>BBBBBBBS FFFFFFS (coeff pair 2)<br>BBBBBBBS FFFFFFS (coeff pair 3)<br>BBBBBBBS FFFFFFS (coeff pair 4)<br>BBBBBBBS FFFFFFS (coeff pair 5) |  |

|                               | MODE x1          | AAAAAAAA PPPPPPPP<br>BBBBBBBS FFFFFFS (coeff pair 0)<br>BBBBBBBBS FFFFFFS (coeff pair 1)<br>BBBBBBBBS FFFFFFS (coeff pair 2)<br>BBBBBBBS FFFFFFS (coeff pair 3)<br>BBBBBBBS FFFFFFFS (coeff pair 4)                                |  |

## Ref Top

| 9/12/20 | 17     | SP0256 Instruction Set                                                                                                                                                                                                  |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | BBBBBBBS FFFFFFS (coeff pair 5)<br>aaaaaaas pppppps (pitch and amplitude interpolation)                                                                                                                                 |

|         | Action | Loads amplitude, pitch, and all coefficient pairs at full 8-bit precision.                                                                                                                                              |

|         | Notes  | • The pitch and amplitude deltas that are available in Mode 01 and 11 are applied <i>every</i> pitch period, not just once. Wraparound may occur. If the Pitch goes to zero, the periodic excitation switches to noise. |

| OPCODE<br>0010              | LOAD_2           | Load Pitch, Amplitude, Coefficients, and Interpolation registers.                                                                                                                                                                                |

|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format                      | RRRR 0010 [data] |                                                                                                                                                                                                                                                  |

| Data<br>Formats,<br>by MODE | MODE 00          | AAAAAA PPPPPPP<br>BBB FFFFS (coeff pair 0)<br>BBB FFFFS (coeff pair 1)<br>BBB FFFFS (coeff pair 2)<br>BBBB FFFFS (coeff pair 3)<br>BBBBBBS FFFFFS (coeff pair 4)<br>aaaaa ppppp (Interpolation register LSBs)                                    |

|                             | MODE Ø1          | AAAAAA PPPPPPP<br>BBB FFFFS (coeff pair 0)<br>BBB FFFFS (coeff pair 1)<br>BBB FFFFS (coeff pair 2)<br>BBBB FFFFFS (coeff pair 3)<br>BBBBBBS FFFFFS (coeff pair 4)<br>BBBBBBBS FFFFFFS (coeff pair 5)<br>aaaaa pppp (Interpolation register LSBs) |

|                             | MODE 10          | AAAAAA PPPPPPP<br>BBBBBB FFFFS (coeff pair 0)<br>BBBBBB FFFFS (coeff pair 1)<br>BBBBBB FFFFFS (coeff pair 2)<br>BBBBBBB FFFFFS (coeff pair 3)<br>BBBBBBBS FFFFFFS (coeff pair 4)<br>aaaaa pppp (Interpolation register LSBs)                     |

|                             | MODE 11          | AAAAAA PPPPPPPP<br>BBBBBB FFFFS (coeff pair 0)<br>BBBBBB FFFFFS (coeff pair 1)<br>BBBBBB FFFFFS (coeff pair 2)                                                                                                                                   |

| 9/1 | 2/2017 | SP0256 Instruction Set                                                                                                                                                                                                                                                                                              |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        | BBBBBBFFFFFS(coeff pair 3)BBBBBBBSFFFFFFS(coeff pair 4)BBBBBBBSFFFFFFS(coeff pair 5)aaaaappppp(Interpolation register LSBs)                                                                                                                                                                                         |

|     | Action | Loads new amplitude and pitch parameters. Also loads a set of new filter coefficients, setting the unspecified coefficients to zero.<br>The exact combination and precision of filter coefficients that are loaded is determined by which prefix is used. Opcode <u>1000</u><br>(SETMODE) provides the prefix bits. |

|     | Notes  | <ul> <li>For all Modes, the Sign bit for B0, B1, B2 and B3 (the B coeffs for pair 0 thru pair 3) has an implied value of 0.</li> <li>This opcode is identical to Opcode <u>1100</u> (LOAD_C), except that it also loads new values into the Amplitude and Pitch Interpolation Registers.</li> </ul>                 |

| OPCODE<br>0011      | SETMSB_3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Load Pitch, Amplitude, MSBs of 3 Coefficients, and Interpolation Registers.                                                 |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Format              | RRRR 0011 [data]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |  |

| Data                | MODE Øx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AAAAAA<br>FFFFS (New F0 MSBs)<br>FFFFS (New F1 MSBs)<br>FFFFS (New F2 MSBs)<br>aaaaa ppppp (Interpolation register LSBs)    |  |

| Formats,<br>by MODE | MODE 1x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AAAAAA<br>FFFFFS (New F0 MSBs)<br>FFFFFS (New F1 MSBs)<br>FFFFFS (New F2 MSBs)<br>aaaaa ppppp (Interpolation register LSBs) |  |

| Action              | Loads new amplitude. Also updates the MSBs of a set of new filter coefficients. The Mode prefix bits controls the update process as noted below. Opcode <u>1000</u> (SETMODE) provides the prefix bits.                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |  |

| Notes               | <ul> <li>When MODE is 00 or 10, the parameter load sets the 5 or 6 MSBs of F0, F1, and F2 from the data provided. F5 and B5 ar to all 0s. All other coefficient bits are unaffected.</li> <li>When MODE is 01 or 11, the parameter load sets the 5 or 6 MSBs of F0, F1, and F2 from the data provided. F5 and B5 ar modified. All other coefficient bits are unaffected.</li> <li>This opcode is identical to Opcodes 0101 (SETMSB_5) and 1010 (SETMSB_A), except that is also includes the Interpolation Registers, and like Opcode 1010 (SETMSB_A), it does not set the Pitch Registers.</li> </ul> |                                                                                                                             |  |

| [ <u>Ref</u> ] [ <u>Top</u> ] |                                                                                                                                                                                                                                                                                                            |                                                                                                                      |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| OPCODE<br>0100                | LOAD_4                                                                                                                                                                                                                                                                                                     | Load Pitch, Amplitude, Coefficients (2 or 3 stages)                                                                  |  |

| Format                        | RRRR 0100 [data]                                                                                                                                                                                                                                                                                           |                                                                                                                      |  |

|                               | MODE 00                                                                                                                                                                                                                                                                                                    | AAAAAA PPPPPPPP<br>BBBB FFFFS (coeff pair 3)<br>BBBBBBS FFFFS (coeff pair 4)                                         |  |

| Data                          | MODE Ø1                                                                                                                                                                                                                                                                                                    | AAAAAA PPPPPPPP<br>BBBB FFFFS (coeff pair 3)<br>BBBBBBBS FFFFFS (coeff pair 4)<br>BBBBBBBS FFFFFFS (coeff pair 5)    |  |

| Formats,<br>by MODE           | MODE 10                                                                                                                                                                                                                                                                                                    | AAAAAA PPPPPPPP<br>BBBBBB FFFFFS (coeff pair 3)<br>BBBBBBBS FFFFFFS (coeff pair 4)                                   |  |

|                               | MODE 11                                                                                                                                                                                                                                                                                                    | AAAAAA PPPPPPP<br>BBBBBB FFFFFS (coeff pair 3)<br>BBBBBBBS FFFFFFS (coeff pair 4)<br>BBBBBBBS FFFFFFS (coeff pair 5) |  |

| Action                        | Loads new amplitude and pitch parameters. Also loads a set of new filter coefficients, setting the unspecified coefficients to 0. The exact combination and precision of filter coefficients that are loaded is determined by which prefix is used. Opcode <u>1000</u> (SETMODE) provides the prefix bits. |                                                                                                                      |  |

| Notes                         | • For all modes, the Sign bit for B0 (the B coefficient for pair 0) has an implied value of 0.                                                                                                                                                                                                             |                                                                                                                      |  |

| [ <u>Ref] [Top]</u> |                  |                                                   |

|---------------------|------------------|---------------------------------------------------|

| OPCODE<br>0101      | SETMSB_5         | Load Pitch, Amplitude, and MSBs of 3 Coefficients |

| Format              | RRRR 0101 [data] |                                                   |

| Data<br>Formats,    |                  | AAAAAA PPPPPPPP<br>FFFS (New F0 MSBs)             |

9/12/2017

| SP0256   | Instruction | Set |

|----------|-------------|-----|

| 51 02 50 | moti action | Jul |

| 9/12 | /2017   |                                                                             |                                                                            | SP0256 Ins                                                                                                               | ruction Set                                                                                                                                                                                                           |

|------|---------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | by mode |                                                                             | FFFFS<br>FFFFS                                                             | (New F1 MSBs)<br>(New F2 MSBs)                                                                                           |                                                                                                                                                                                                                       |

|      |         | MODE 1x                                                                     | AAAAAA PPPPP<br>FFFFFS<br>FFFFFS<br>FFFFFS                                 | PPP<br>(New F0 MSBs)<br>(New F1 MSBs)<br>(New F2 MSBs)                                                                   |                                                                                                                                                                                                                       |

|      | Action  | Loads new amplitude the update process as                                   | and pitch para<br>noted below. (                                           | umeters. Also updates the M<br>Dpcode <u>1000</u> (SETMODE) prov                                                         | ISBs of a set of new filter coefficients. The Mode prefix bits controls vides the prefix bits.                                                                                                                        |

|      | Notes   | <ul> <li>set to all 0s. Al</li> <li>When MODE is modified. All o</li> </ul> | l other coeffici<br>01 or 11, the pa<br>ther coefficien<br>identical to Op | ent bits are unaffected.<br>arameter load sets the 5 or 6<br>t bits are unaffected.<br>bcodes <u>0011</u> (SETMSB_3) and | $^{6}$ MSBs of F0, F1, and F2 from the data provided. F5 and B5 are $^{6}$ MSBs of F0, F1, and F2 from the data provided. F5 and B5 are not $1010$ (SETMSB_A), only Pitch <i>is</i> modified, and unlike Opcode 0011, |

### [Ref] [Ton]

| OPCODE<br>0110      | SETMSB_6         | Load Amplitud                           | e and MSBs of 2 or 3 Coeffcients                      |

|---------------------|------------------|-----------------------------------------|-------------------------------------------------------|

| Format              | RRRR 0110 [data] |                                         |                                                       |

|                     | MODE 00          | AAAAAA<br>FFFFS<br>FFFFS                | (New F3 6 MSBs)<br>(New F4 6 MSBs)                    |

| Data<br>Formata     | MODE Ø1          | AAAAAA<br>FFFFFS<br>FFFFFFS<br>FFFFFFFS | (New F3 6 MSBs)<br>(New F4 6 MSBs)<br>(New F5 8 MSBs) |

| Formats,<br>by MODE | MODE 10          | AAAAAA<br>FFFFFS<br>FFFFFFS             | (New F3 7 MSBs)<br>(New F4 8 MSBs)                    |

|                     | MODE 11          | AAAAAA<br>FFFFFFS<br>FFFFFFS<br>FFFFFFS | (New F3 7 MSBs)<br>(New F4 8 MSBs)<br>(New F5 8 MSBs) |

| 9/12/2017 |

|-----------|

|-----------|

| Action | Loads new amplitude and pitch parameters. Also updates the MSBs of a set of new filter coefficients. The MODE prefix bits controls the update process as noted below. Opcode <u>1000</u> (SETMODE) provides the prefix bits.                                                                                                                                                                                                                                                                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Notes  | <ul> <li>For MODE 00 and 10, coefficients B5 and F5 are set to zero.</li> <li>For MODE 01 and 11, coefficient F5 is set from the last 8 bits of the data provided, and B5 is not modified.</li> <li>For MODE 00 and 01, the 6 MSBs of F3 and F4 are set from the first 12 bits provided. The other bits of F3 and F4 are not modified.</li> <li>For MODE 10 and 11, the 7 MSBs of F3 and the 8 MSBs of F4 are set from the first 12 bits provided. The LSB of F3 is not modified.</li> </ul> |

| OPCODE<br>0111 | JMP                                           | Jump to 12-bit PAGE-Relative Address                                                                                                                                                                                                                                                                                                             |

|----------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format         | LLLL 0111 LLLLLLL                             |                                                                                                                                                                                                                                                                                                                                                  |

| Action         | instruction jumps to the come from the JMP in | The specified 12-bit address relative to the 4K page number specified by the PAGE register. That is, the JMP he location PAGE LLLL LLLLLLL, where the upper four bits come from the PAGE register and the lower 12 bits instruction.<br>E register defaults to the value 0001 (\$1). The PAGE register may be set using the SETPAGE instruction, |

| [D of] | ГЛ | on]       |

|--------|----|-----------|

|        |    | <u>op</u> |

| OPCODE<br>1000 | SETMODE                                                                                                                                                                                                                                                                                            | Set the MODE bits and Repeat MSBs                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Format         | RRMM 1000                                                                                                                                                                                                                                                                                          |                                                                                                   |

| Action         | Serves as a prefix to many other instructions. The upper two bits of the immediate constant are loaded into the upper two bits of the 6-bit repeat register. These two bits combine with the four LSBs that are provided by most parameter-load instructions to provide longer repetition periods. |                                                                                                   |

|                | The two MM bits select the data format / coefficient count for many of the parameter load instructions.                                                                                                                                                                                            |                                                                                                   |

|                | This opcode is known                                                                                                                                                                                                                                                                               | n to have <i>no</i> effect on JMP/JSR instructions and JMP/JSR instructions have no effect on it. |

| Notes | • The MM mode bits are <i>sticky</i> , meaning that they stay in effect until the next Opcode <u>1000</u> (SETMODE) instruction. The RR repeat bits are not, however. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                       |

| OPCODE<br>1001      | DELTA_9          | Delta update Amplitude, Pitch and 5 or 6 Coefficients                                                                                                                                                                                 |

|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format              | RRRR 1001 [data] |                                                                                                                                                                                                                                       |

|                     | MODE 00          | aaasppps(Amplitude 6 MSBs, Pitch LSBs.)bbsffs(B0 4 MSBs, F0 5 MSBs.)bbsffs(B1 4 MSBs, F1 5 MSBs.)bbsffs(B2 4 MSBs, F2 5 MSBs.)bbsfffs(B3 5 MSBs, F3 6 MSBs.)bbsfffs(B4 6 MSBs, F4 6 MSBs.)                                            |

| Data                | MODE Ø1          | aaaspppps(Amplitude 6 MSBs, Pitch LSBs.)bbsffs(B0 4 MSBs, F0 5 MSBs.)bbsffs(B1 4 MSBs, F1 5 MSBs.)bbsffs(B2 4 MSBs, F2 5 MSBs.)bbsfffs(B3 5 MSBs, F3 6 MSBs.)bbsfffs(B4 6 MSBs, F4 6 MSBs.)bbbsfffs(B5 8 MSBs, F5 8 MSBs.)            |

| Formats,<br>by MODE | MODE 10          | aaasppps(Amplitude 6 MSBs, Pitch LSBs.)bbbsfffs(B0 7 MSBs, F0 6 MSBs.)bbbsfffs(B1 7 MSBs, F1 6 MSBs.)bbbsfffs(B2 7 MSBs, F2 6 MSBs.)bbbsffffs(B3 7 MSBs, F3 7 MSBs.)bbbsffffs(B4 8 MSBs, F4 8 MSBs.)                                  |

|                     | MODE 11          | aaasppps(Amplitude 6 MSBs, Pitch LSBs.)bbbsfffs(B0 7 MSBs, F0 6 MSBs.)bbbsfffs(B1 7 MSBs, F1 6 MSBs.)bbbsfffs(B2 7 MSBs, F2 6 MSBs.)bbbsffffs(B3 7 MSBs, F3 7 MSBs.)bbbsffffs(B4 8 MSBs, F4 8 MSBs.)bbbbsffffs(B5 8 MSBs, F5 8 MSBs.) |

| Action              | 1 <b>1</b>       | ate, adding small 2s complement numbers to a series of coefficients. The 2s complement updates for the ents only update some of the MSBs the LSBs are unaffected. The exact bits which are updated are noted                          |

17

| Notes | <ul> <li>The delta update is applied exactly once, as long as the repeat count is at least 1. If the repeat count is greater than 1, the updated value is held through the repeat period, but the delta update is not reapplied.</li> <li>The delta updates are applied to the 8-bit encoded forms of the coefficients, not the 10-bit decoded forms.</li> <li>Normal 2s complement arithmetic is performed, and no protection is provided against overflow. Adding 1 to the largest value for a bit field wraps around to the smallest value for that bitfield.</li> <li>The update to the amplitude register is a normal 2s complement update to the <i>entire</i> register. This means that any carry/borrow from the mantissa will change the value of the exponent. The update doesn't know anything about the format of that register.</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPCODE           1010       | SETMSB_A         | Load Amplitude and MSBs of 3 Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Format                      | RRRR 1010 [data] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Data<br>Formats,<br>by MODE | MODE Øx          | AAAAAA<br>FFFFS (New F0 MSBs)<br>FFFFS (New F1 MSBs)<br>FFFFS (New F2 MSBs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                             | MODE 1x          | AAAAAA<br>FFFFS (New F0 MSBs)<br>FFFFFS (New F1 MSBs)<br>FFFFFS (New F2 MSBs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                             | Action           | Loads new amplitude. Also updates the MSBs of a set of new filter coefficients. The MODE prefix bits controls the update process as noted below. Opcode <u>1000</u> (SETMODE) provides the prefix bits.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                             | Notes            | <ul> <li>When MODE is 00 or 10, the parameter load sets the 5 or 6 MSBs of F0, F1, and F2 from the data provided. F5 and B5 are set to all 0s. All other coefficient bits are unaffected.</li> <li>When MODE is 01 or 11, the parameter load sets the 5 or 6 MSBs of F0, F1, and F2 from the data provided. F5 and B5 are not modified. All other coefficient bits are unaffected.</li> <li>This opcode is identical to Opcodes 0011 (SETMSB_3) and 0101 (SETMSB_5), except that Pitch is <i>not</i> modified, and the Interpolation Registers are <i>not</i> set.</li> </ul> |  |  |

| OPCODE<br>1011 | JSR                                                                                                                                                                                                                                                                                             | Jump to Subroutine (12-bit PAGE-Relative Address)                                                                                                                                                                                                                                              |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Format         | LLLL 1011 LLLLLLL                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                |  |  |  |

|                | Performs a jump to the specified 12-bit address relative to the 4K page number specified by the PAGE register. That is, the JMP instruction jumps to the location PAGE LLLL LLLLLLL, where the upper four bits come from the PAGE register and the lower 12 bits come from the JSR instruction. |                                                                                                                                                                                                                                                                                                |  |  |  |

| Action         | Opcode <u>0000</u> .<br>This variant pushes th                                                                                                                                                                                                                                                  | E register defaults to the value 0001 (\$1). The PAGE register may be set using the SETPAGE instruction,<br>the byte-aligned return address onto the PC stack. The previous contents of the PC stack are lost, as the PC<br>ty deep. To return to the next instruction, use Opcode 0000 (RTS). |  |  |  |

| [ <u>Kei</u> ] [ <u>lop</u> ] |                         |                                                                                        |                                                                                                       |

|-------------------------------|-------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| OPCODE<br>1100                | LOAD_C Load Pitch, Ampl |                                                                                        | plitude, Coefficients (5 or 6 stages)                                                                 |

| Format                        | RRRR 1100 [data]        |                                                                                        |                                                                                                       |

| Data<br>Formats,<br>by MODE   | MODE 00                 | AAAAAA PPPPPP<br>BBB FFFFS<br>BBB FFFFS<br>BBB FFFFS<br>BBBB FFFFS<br>BBBBBBBS FFFFFS  | (coeff pair 0)<br>(coeff pair 1)<br>(coeff pair 2)<br>(coeff pair 3)                                  |

|                               | MODE 01                 | AAAAAA PPPPPP<br>BBB FFFFS<br>BBB FFFFS<br>BBB FFFFS<br>BBBB FFFFFS<br>BBBBBBBS FFFFFF | <pre>(coeff pair 0)<br/>(coeff pair 1)<br/>(coeff pair 2)<br/>(coeff pair 3)<br/>(coeff pair 4)</pre> |

|                               | MODE 10                 | AAAAAA PPPPPP<br>BBBBBB FFFFS<br>BBBBBBB FFFFS<br>BBBBBBB FFFFFS                       | (coeff pair 0)<br>(coeff pair 1)                                                                      |

| 9/12/2017 |                                                                                                                                                                                                                                                                                                               |                                                                                                  | SP0256 Instruction Set                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|           |                                                                                                                                                                                                                                                                                                               |                                                                                                  | pair 3)<br>pair 4)                                                                 |

|           | MODE 11                                                                                                                                                                                                                                                                                                       | BBBBBB FFFFFS (coeff<br>BBBBBB FFFFFS (coeff<br>BBBBBB FFFFFFS (coeff<br>BBBBBBBS FFFFFFS (coeff | pair 0)<br>pair 1)<br>pair 2)<br>pair 3)<br>pair 4)<br>pair 5)                     |

| Action    | Loads new amplitude and pitch parameters. Also loads a set of new filter coefficients, setting the unspecified coefficients to zero. The exact combination and precision of filter coefficients that are loaded is determined by which prefix is used. Opcode <u>1000</u> (SETMODE) provides the prefix bits. |                                                                                                  |                                                                                    |

| Notes     | • For all values of                                                                                                                                                                                                                                                                                           | f MODE, the Sign bit for B0, B1                                                                  | , B2 and B3 (the B coefficients for pair 0 thru pair 3) has an implied value of 0. |

| DELTA_D          | Delta update Amplitude, Pitch and 2 or 3 Coefficients |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRRR 1101 [data] |                                                       |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                           |

| MODE 00          | aaas                                                  | pppps                                                                                                                                                                                                                              | (Amplitude 6 MSBs, Pitch LSBs.)                                                                                                                                                                                                                                                                                           |

|                  | bbs                                                   | fffs                                                                                                                                                                                                                               | (B3 5 MSBs, F3 6 MSBs.)                                                                                                                                                                                                                                                                                                   |

|                  | bbbs                                                  | fffs                                                                                                                                                                                                                               | (B4 7 MSBs, F4 6 MSBs.)                                                                                                                                                                                                                                                                                                   |

| MODE 01          | aaas                                                  | pppps                                                                                                                                                                                                                              | (Amplitude 6 MSBs, Pitch LSBs.)                                                                                                                                                                                                                                                                                           |

|                  | bbs                                                   | fffs                                                                                                                                                                                                                               | (B3 5 MSBs, F3 6 MSBs.)                                                                                                                                                                                                                                                                                                   |

|                  | bbbs                                                  | fffs                                                                                                                                                                                                                               | (B4 7 MSBs, F4 6 MSBs.)                                                                                                                                                                                                                                                                                                   |

|                  | bbbbs                                                 | ffffs                                                                                                                                                                                                                              | (B5 8 MSBs, F5 8 MSBs.)                                                                                                                                                                                                                                                                                                   |

| MODE 10          | aaas                                                  | pppps                                                                                                                                                                                                                              | (Amplitude 6 MSBs, Pitch LSBs.)                                                                                                                                                                                                                                                                                           |

|                  | bbbs                                                  | ffffs                                                                                                                                                                                                                              | (B3 7 MSBs, F3 7 MSBs.)                                                                                                                                                                                                                                                                                                   |

|                  | bbbbs                                                 | ffffs                                                                                                                                                                                                                              | (B4 8 MSBs, F4 8 MSBs.)                                                                                                                                                                                                                                                                                                   |