### SYNTHETIC SPEECH

FOR PERSONAL COMPUTERS

by Joseph E. Hébert

date 5 August, 1991

project supervisor Mr. Jack Burson

faculty committee

Mr. Jack Burson

Mr. Wilbur H. Gruver

Dr. Russell L. Heiserman

### **Abstract**

This document accompanies the project outlined within. It was prepared for the course TECHNOLOGY 420, a required course for the completion of a Bachelor of Science degree in the Department of Electronics Technology, College of Engineering and Technology, at McNeese State University.

The text of this report is organized into chapters as prescribed by the course requirements. Some chapters are subdivided into Sections and/or Paragraphs as deemed necessary by the author. Note that, as it applies to the organizational structure of this document, the term 'Paragraph' refers to the lessermost subdivision of the textual content. This is similar to, but distinct from, the traditional definition of the term.

The Introduction chapter discusses the development of computer technology as it relates to the individual user. A historical review and a projection of near-future developments lend consideration to the potential impact of synthetic speech on the computer user.

The DESIGN OBJECTIVES chapter prescribes the author's intentions pertinent to this project.

The RESEARCH OF LITERATURE chapter discusses the considerations necessary for the implementation of synthetic speech, as well as the details of the chip-set chosen for this project and how they address the necessary considerations.

The CIRCUIT DESIGN chapter discusses the considerations made in choosing the circuitry components and configurations implemented in this project.

The THEORY OF OPERATION chapter discusses the operation of the unit built for this project. An overview of the unit as a system is given prior to discussing the details of the various sub-circuits.

The TESTING AND RESULTS chapter discusses each of the design problems encountered in the development of this project and, when applicable, how they were corrected.

The FINAL ASSEMBLY chapter details the finished unit in terms of how it is housed, as well as how interface connections are provided.

The CONCLUSIONS AND RECOMMENDATIONS chapter discusses the performance of the finished unit relative to considerations which should be made when configuring the unit for a given

application. Also discussed are techniques for constructing double sided printed circuit boards and silkscreen printing. This chapter also details the cost of the project.

The APPENDICES contain a bibliographical listing of the technical literature referred to in this report, a complete set of schematics, all trace patterns and component overlays, and a source code listing of the special OrCad® component library compiled for this project.

### Registered Trademarks

Apple® and MacIntosh® are registered trademarks of Apple Computers, Inc.

AutoCado is a registered trademark of AutoDesk, Inc.

AutoTrax® is a registered trademark of Protel, Inc.

CSAM® is a registered trademark of Computer Support Corporation, Inc.

General Instruments® is a registered trademark of General Instruments, Inc.

IBM. AS/4000, and PS/20 are registered trademarks of International Business Machines, Inc.

Intel® is a registered trademark of Intel, Inc.

Microchip® is a registered trademark of Microchip, Inc.

Motorola® is a registered trademark of Motorola, Inc.

MS-DOS® is a registered trademark of Microsoft Corporation.

OrCado is a registered trademark of OrCad Systems Corporation.

QAPluso is a registered trademark of DiagSoft, Inc.

Tandyo and Radio Shacko are registered trademarks of Tandy, Inc.

Texas Instruments® and TI99-A® are registered trademarks of Texas Instruments, Inc.

Toshiba® is a registered trademark of Toshiba American, Inc.

Ulanoo and Blue Polyo are registered trademarks of Ulano Corporation.

WordPerfect® is a registered trademark of WordPerfect Corporation.

Zilogo is a registered trademark of Zilog, Inc.

### Acknowledgments

Though I did not have any collaborators in this project, I do feel compelled to extend thanks to several people who made it possible for me to be where I am today.

First, I owe a debt of thanks to Mr. Charles Prejean. Four years ago, I walked into Mr. Prejean's office and announced that I wanted to earn two degrees, one in physics and one in electronics. As if to redefine the term *audacity*, I told Mr. Prejean that I had only a ninth-grade education and a GED, that my ultimate goal was to earn my doctorate in physics, (this despite having never had a physics course), and the only way I could afford this dream was with financial assistance. I then asked Mr. Prejean if he could arrange a scholarship, and in the course of a single phone call it was done. I want to thank Mr. Prejean for abandoning reason and making that phone call.

This brings up my second debt of thanks. Were it not for the philanthropy of H.C. Drew, and the scholarship that bears his name, I truly would not have been afforded the opportunity to pursue my dream.

But the road from there to here was not as easy as the one phone call that made it possible. It has taken much work, not only on my part but on the parts of many. I am referring to part of that group of individuals who have devoted their lives to helping those of us who have chosen to pursue the dream of an education; I am referring to my instructors. During the past three and a half years I have benefitted from the efforts of many instructors, and I would like to thank them all.

Finally, I must thank God for bringing me to the point I have reached. Were it not His will, I could never have come this far, nor would I have had reason to.

## Table of Contents

| CHAPTER   | SECTION        | Paragraph                         | page no. |

|-----------|----------------|-----------------------------------|----------|

| Abstra    | act            |                                   | i        |

| Regist    | ered Trademark | cs                                | iii      |

|           |                |                                   |          |

|           |                |                                   |          |

| Table     | of Tables      |                                   | viii     |

| INTRODUC  | TION           |                                   | 1        |

|           | A HISTORICA    | L OVERVIEW                        | 2        |

|           |                | COMPUTERS                         |          |

|           | ARTIFICIAL I   | NTELLIGENCE                       | 3        |

|           | SYNTHETIC S    | PEECH                             | 4        |

|           | APPLICATION    | S                                 | 5        |

| DESIGN O  | BJECTIVES .    |                                   | 7        |

| RESEARCH  | OF LITERA      | TURE                              | 9        |

|           | THE NATURE     | OF SPEECH                         | 10       |

|           | THE SPO256     | AL2                               | 13       |

|           | THE CTS256     | A-AL2                             | 15       |

|           |                | External ROM                      | 16       |

|           |                | External RAM                      | 16       |

|           |                | Parallel Data Port                | 16       |

|           |                | Switch Selectable UART Parameters | 17       |

|           |                | Pinout Information                | 17       |

| CIRCUIT D | ESIGN          |                                   | 20       |

|           | CTS256A-AL     | 2                                 | 21       |

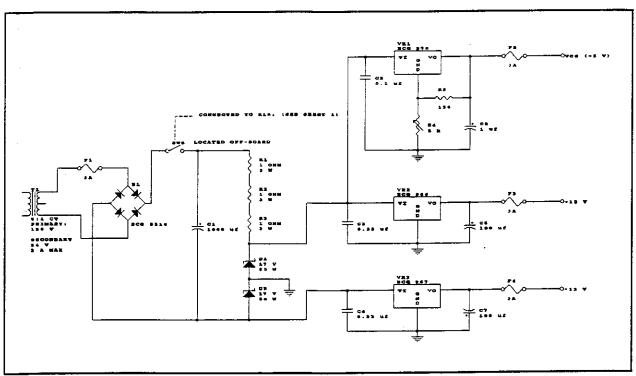

|           | POWER SUPP     | LY                                | 23       |

| THEORY OF OPERATIO | N                                          | . 27 |

|--------------------|--------------------------------------------|------|

|                    | ERVIEW                                     |      |

| System Det         | AILS                                       | . 29 |

|                    | Parallel Port                              | . 30 |

|                    | Serial Port                                | . 31 |

|                    | Switch Selectable UART Parameters          | . 32 |

|                    | External RAM                               |      |

|                    | Addressing the SPO256-AL2                  | . 34 |

|                    | SPO256-AL2 Output                          | . 35 |

| TESTING AND RESULT | S                                          | . 36 |

|                    | Product Support                            | . 37 |

|                    | Product Design                             | . 38 |

|                    | The Address Bus                            |      |

|                    | The Parallel Port                          |      |

|                    | The Serial Port                            |      |

|                    | External ROM                               |      |

|                    | An MS-DOS® Bug                             |      |

| FINAL ASSEMBLY     | · • • • • • • • • • • • • • • • • • • •    |      |

| CONCLUSIONS AND RI | ECOMMENDATIONS                             | . 45 |

| Unit Perfo         | RMANCE                                     | . 46 |

|                    | DED BOARD CONSTRUCTION                     |      |

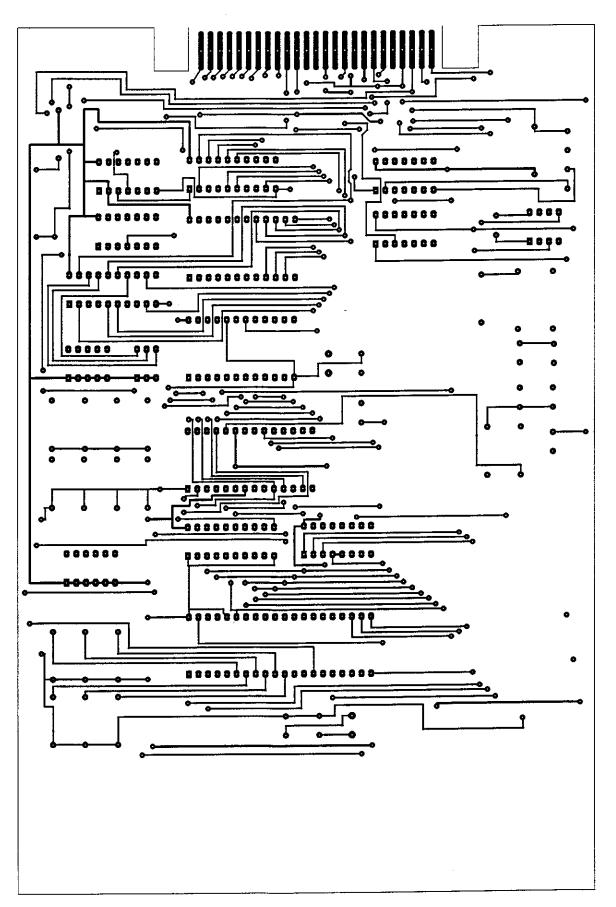

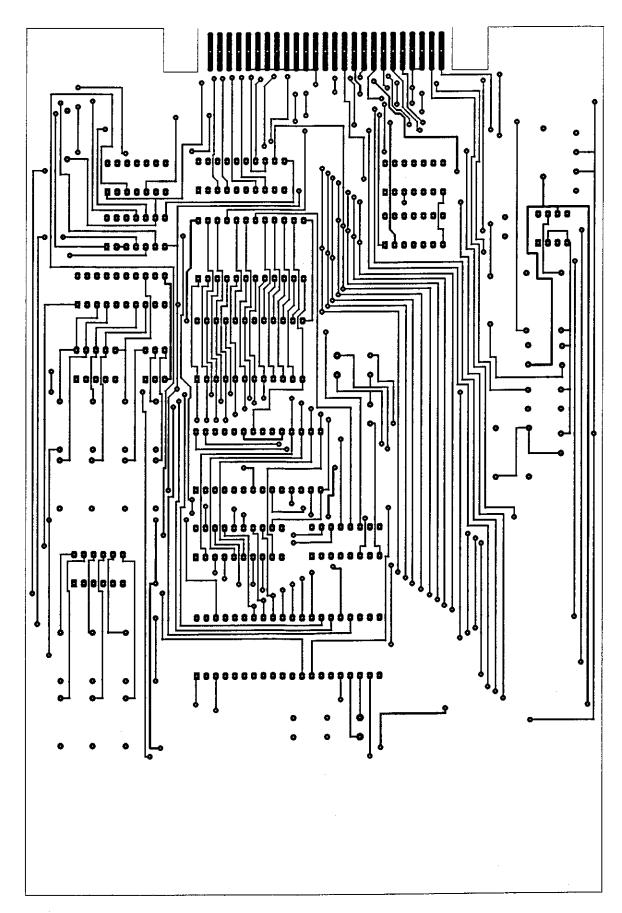

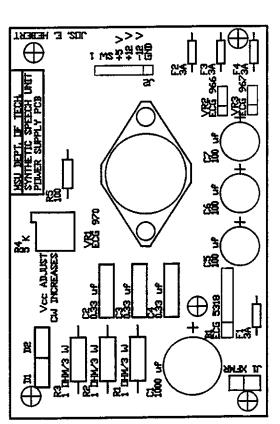

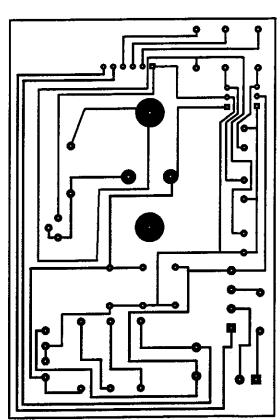

|                    | Computer Generated Trace Patterns          |      |

|                    | Developing and Etching Double Sided Boards | . 49 |

|                    | Vias and Thru-continuity                   | . 51 |

| SILKSCREEN         | Printing                                   |      |

| Project Co         | ST                                         | . 54 |

| APPENDICES         | · · · · · · · · · · · · · · · · · · ·      | . 55 |

| APPENDIX A: Refer  | ences                                      | . 56 |

|                    | natics                                     |      |

|                    | Patterns and Component Overlays            |      |

|                    | e Code for OrCad® Library                  |      |

## Table of Illustrations

| Figu       | JRE                                                          | page no. |

|------------|--------------------------------------------------------------|----------|

| 1:         | Points of occlusion for consonant phonemes                   | 11       |

| 2:         | Pinouts of the SPO256-AL2                                    | 14       |

| 3:         | Pinouts of the CTS256A-AL2/PIC7041                           | 17       |

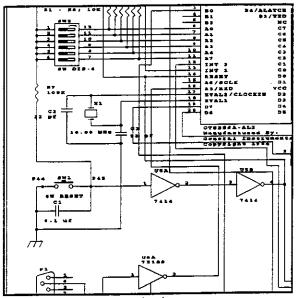

| <b>4</b> : | Hardware reset circuitry                                     | 21       |

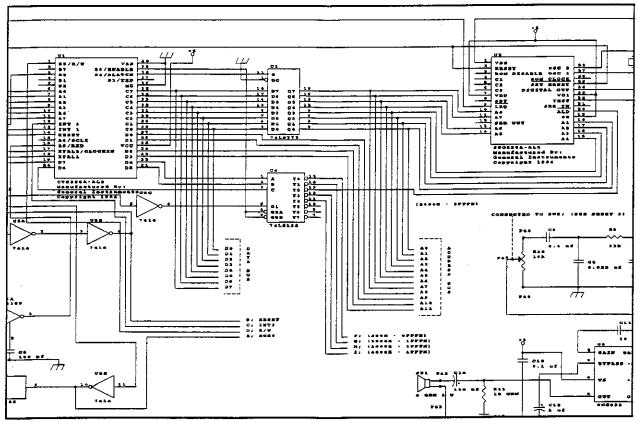

| <b>5</b> : | Data/Address bus circuitry                                   |          |

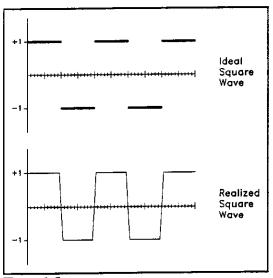

| 6:         | Square waves                                                 | 24       |

| 7:         | Power supply circuitry                                       | 26       |

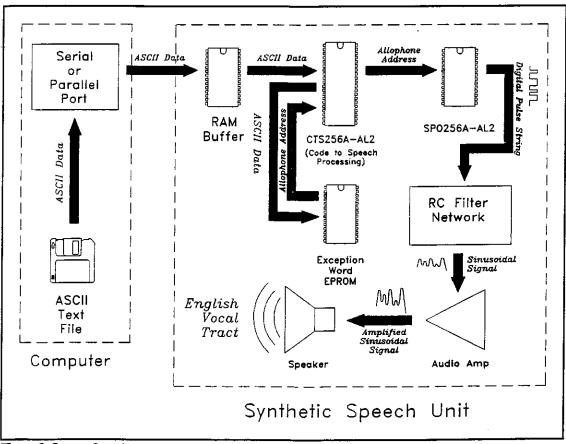

| 8:         | System flow chart                                            | 28       |

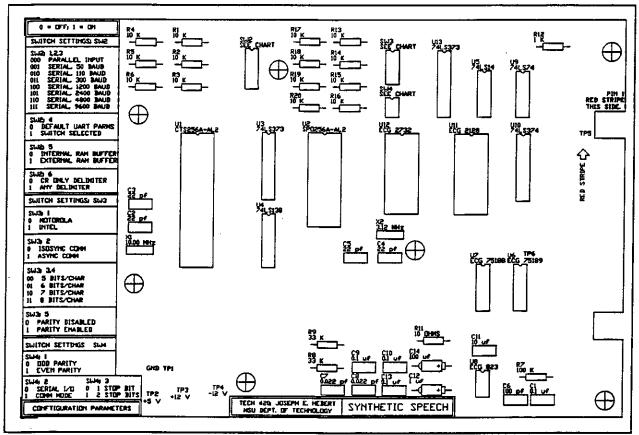

| 9:         | Component layout of main circuit board                       | 42       |

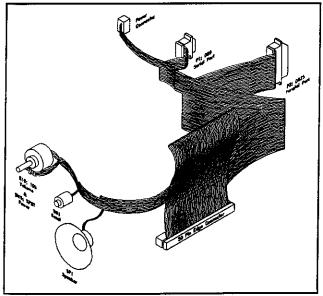

| 10:        | Wiring harness for main circuit board                        | 42       |

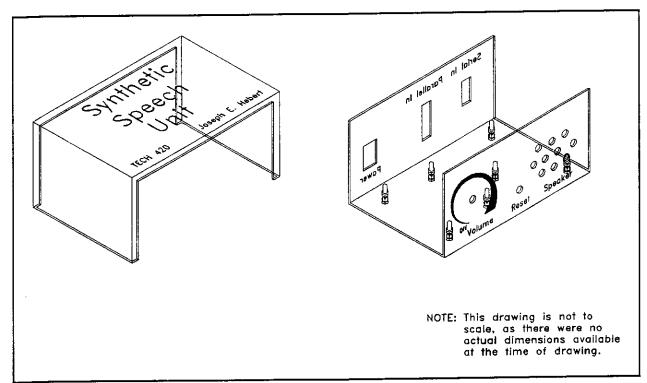

| 11:        | Housing for main circuit board                               |          |

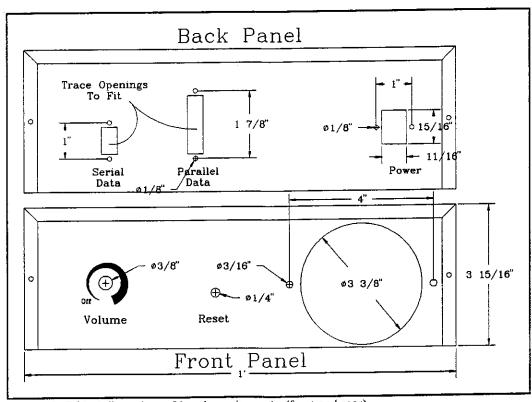

| 12:        | Critical dimensions of housing unit panels, (front and rear) |          |

| 13:        | Registration limit                                           | 47       |

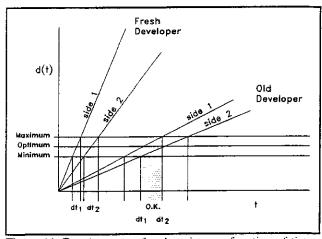

| 14:        | Development of etch-resist as a function of time             | 50       |

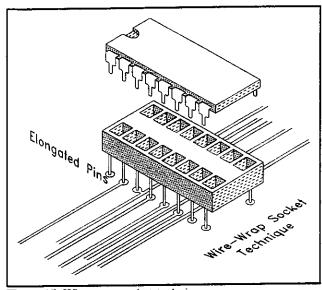

| 15:        | Wire-wrap socket technique                                   | 51       |

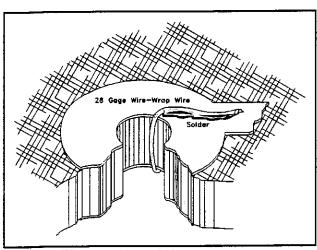

| 16:        | Wire-wrap wire technique                                     | 51       |

## Table of Tables

| TABL        | LE P                                          | age n | o. |

|-------------|-----------------------------------------------|-------|----|

| 1:          | Vowel Phonemes                                | 1     | 1  |

| 2:          | Consonant Phonemes                            | 1     | 2  |

| 3:          | Allophones of the SPO256-AL2                  | 1     | 3  |

| 4:          | Port A Pin Configuration Information          | 1     | 8  |

| 5:          | UART Bits/Character Configuration Information | 3     | 3  |

| <b>6:</b> - | Project Cost                                  | 5     | 54 |

# Introduction

The focus of this research project is the implementation of synthetic speech for personal computers. Though the focus here is on MS-DOS® based computers, it is important to understand that the same principles discussed in this report will apply to any computer. While a MacIntosh® would require different hardware specifications, and a mainframe would require the use of EBCDIC text encoding instead of ASCII, the general principles will remain constant.

In addition to understanding the principles of synthetic speech, the reader would do well to understand the broader ramifications of the same. Toward that end, this report will begin by considering how the development of personal computers has led to the advent of synthetic speech in a *natural* way. Though the need for, and benefits of, synthetic speech may be intuitively obvious, a more deliberate consideration of the matter will be given here.

### § A HISTORICAL OVERVIEW §

Not many years ago there was a clear distinction between mainframe computers and personal, or desktop, computers. Size notwithstanding, personal computers were little more than toys. The TI99-A® came equipped with 8 kilobytes of system RAM, a keyboard, and little else. A standard television was required to serve as the CRT, and saving a program required the addition of a special cable and a cassette player/recorder. Though these *toys* were little more than novelties, they did serve to introduce the individual to computers.

But technology is never static, and computer technology is by no means an exception. Developments have made the distinction between mainframes and desktops much less significant, even blurred. With the advent of ULSI microchips, desktop computers are now afforded microprocessors capable of addressing RAM in the gigabyte range and memory chips capable of providing it. Fixed magnetic storage disks with capacities of hundreds of megabytes are common. Advanced operating systems allow this new-found capability to be exploited with true multitasking and networking.

Even the distinction of size has been blurred. IBM® now sells a mainframe, the AS/400®, which is only slightly larger than their PS/2® tower models.

Of course, this new-found power would be of no use without software, and companies have sprung up to meet the need. Packages are readily available that allow people to solve advanced mathematical equations, draw architectural designs, or manage anything from a rental property to a check book.

As is evidenced by this report, instead of typing a term paper a student can now publish one, complete with artwork and illustrations. This report was published with WordPerfect®, version 5.1, and the artwork was produced with AutoCad® and CSAM®. The schematics at the back of this report were drawn with OrCad®, and the trace pattern that eventually became the circuit board which is the subject of this project was produced with AutoTrax®.

### § PEOPLE AND COMPUTERS §

But what good is all of this capability if people can't use it? This has been a driving question throughout the development of computers. The industry coined a phrase in answer to that question; They call it making computers user-friendly. A secretary doesn't have to understand ASCII encoding to write a letter, a programmer doesn't have to understand two's-compliment arithmetic to make a computer do subtraction, and a systems analyst doesn't have to understand flip flops or transistors in order to address memory.

Instead of being concerned with the true nature of whatever aspect of the computer an individual is working with, it is often sufficient to think, or understand, in terms of an analogy. A perfect example is the programmer thinking of five volts as a one-bit, and zero volts as a zero-bit. Many programmers don't even know what a volt is.

One consequence of this is the perception high-end users have of the computer as a whole. Most have come to think of the computer as being analogous to intelligent. The majority of people who work with computers have even lost sight of the distinction between the hardware and software. A clerical worker key-entering a formula into a spreadsheet cell perceives that the computer simply knows how to perform the calculation. Of course, everyone knows that "computers are stupid," but that statement is becoming less and less obvious.

### § ARTIFICIAL INTELLIGENCE §

For years now computer scientists have been researching artificial intelligence. The concept has become so commonplace that it is known simply by its initials, AI. And the reasoning behind the quest is sound. The less expertise that is required to use a computer, the more useful the computer will be. AI is the ultimate *user-friendliness*. But how far into the future is AI? The answer depends on how AI is defined. Consider the following definitions:

Intelligence: 1: The ability to learn or understand.

2: Information.

Ignorance: 1: Lacking knowledge.

Knowledge: 1: Understanding gained by experience.

2: Range of information.

Learn: 1: Gain knowledge by study or experience.

If intelligence is simply information, then computers are intelligent by design. Their purpose is to process and store information.

But that isn't what is meant by AI. At the software level, AI has existed for some time now, though it is still not commonplace. Database managers have been written that use NQL, or natural query language, (NL for short). Instead of utilizing a well-defined syntax, natural language software packages are programmed to pick out key terms in a command. As defined above, these packages learn. A given individual will tend to habitually ask the same questions in the same way. These habits are retained in and by the software for reference so that in time it will become more efficient.

In that some programs have the ability to gain knowledge through experience, AI exists today. Of course, it's still a matter of the software that has this quality, not the computer. Nonetheless, one key word that appears in the above definitions remains unsatisfied. Neither the computer, nor the software, has understanding. Understanding implies consciousness, and computers are simply machines. It is imperative to remember that the key word in artificial intelligence is artificial, not intelligence.

That being understood, one question remains. How closely can machine intelligence approximate human intelligence?

### § SYNTHETIC SPEECH §

Anyone who has ever seen an episode of Star Trek has seen the vision of an intelligent computer. The ship's computer has no keyboard or CRT. It is accessed by simply addressing it verbally. Output from the computer is channeled through the ship's intercom. So common is this image to Star Trek devotees that one of the movie sequels contained a comedic scene in which Scottie, (the Chief Engineer), attempted to access a twentieth century Macintosh by using the mouse as a microphone. Will four centuries make that much difference in our perceptions? How far into the future is verbal interaction between users and computers?

Directory assistance gives out phone numbers via a computerized voice. Many children have listened to Teddy Ruxpin's digital voice. Voice mail and automated telephone services use digitally recreated voices. These are all applications utilizing computerized voices as a means of outputting data to the user that are employed today.

But if these examples are considered examples of AI, then it is also necessary to include tape recorders and phonographs as examples of AI. Clearly that is not the case, nor are these examples of true AI. Each of these use a member of the Toshiba® TC88xxx family of voice recording devices. The speech output is computer controlled, but it first had to be recorded into the computer by a human voice. In order to consider computer generated speech as even an early development of AI, that speech should be completely computer generated. The vocal tract, (the word or phrase), should be constructed by the computer, not just replayed.

One measure that is used to judge the intelligence of humans is literacy<sup>1</sup>, at least to the extent that the ability to read affords people a greater ability to learn. And this is the subject of this research project, to explore the current limitations of enabling personal computers to read written text. If a computer could construct and speak a vocal tract from a text file, with some degree of accuracy, that would be true synthetic speech as well as a much closer approximation of intelligence at the hardware level.

The technology for true synthetic speech exists today, as does the technology for speech recognition, at least in the early developmental stages. True speech synthesis involves dissecting verbal language into fundamental components, and then establishing a relationship with the textual, (or written), language. This allows the computer to generate vocal tracts which were never uttered by a human voice.

Far from being nothing more than the stuff of science fiction, there are real markets for such technology. It isn't necessary to develop the kind of verbal interaction that exists on the star ship Enterprise, or even full vocal interaction, to begin realizing benefits. Simply enabling a computer to output data verbally would prove very beneficial.

### § APPLICATIONS §

Perhaps the most obvious benefactors of such technology would be the visually impaired. With a high resolution scanner, a refined optical character recognition program, (OCR), and a

<sup>&</sup>lt;sup>1</sup> The distinction between education and intelligence is fully acknowledged by the author at this point.

computer capable of synthetic speech, blind people could read their own mail, books, or magazines. There would be no need for special audio recordings of books, and braille could become a lost art.

But the blind certainly wouldn't be the only ones to benefit from such technology. Industry is just beginning to realize some of the hazards associated with computers and computer terminals. Apple® has developed a special CRT that limits the electromagnetic radiation it emits. Some cities are beginning to legislate the number of hours workers can spend at a computer terminal, and revising health codes to prescribe required lighting conditions. Other companies are trying to develop more ergonomically suitable keyboards and mice. This because of a noted increase in the incidence of carpal tunnel syndrome<sup>2</sup> in computer operators.

Consider a device such as the one outlined in this report. It is capable of accepting input in the form of ASCII text strings and converting it into verbal output. If output to the CRT was simultaneously sent to this device, typists and data entry clerks would no longer be dependent on their CRTs to detect their errors. This would enable them to simply turn off their CRTs for much, if not most, of their daily routine. Considering that such a device could be developed with hardware that is currently available and inexpensive, it would certainly be preferable to rewiring the office lighting to meet new health codes. It could also eliminate the need for additional employees to make up for reduced work hours.

From a more futuristic perspective, accommodating verbal input could all but eliminate the need for a keyboard. Could this be accomplished today? Perhaps not, but Toshiba® has introduced voice recognition devices with limited capabilities. The TC8861F/TC8862F/TMP80C50AU chip-set allows for up to 78 words, (a word can be any utterance limited to some maximum time duration), of recognition. This can be either speaker independent, or for the security conscious, speaker dependent. While this is not sufficient to eliminate the keyboard for data input, it would certainly be sufficient for verbal control of the operating system. Considering that the keyboard is the cause of the increase in carpal tunnel syndrome, and considering the expense of corrective surgeries and increased insurance premiums, it would likely be easy to justify financing the research needed to further this technology.

<sup>&</sup>lt;sup>2</sup> Carpal Tunnel Syndrome: A disorder in which the nerve passing through the carpal tunnel, (the wrist), is inflamed by friction with the bone. It can result in varying degrees of disability, depending on the severity of the inflammation. Carpal tunnel syndrome is not self healing since the result of the stimulus, the inflammation, aggravates the stimulus which caused it. For this reason, carpal tunnel syndrome normally requires orthopedic surgery for correction.

# Design Objectives

The project outlined in this report is designed around the General Instrument® chip-set, CTS256A-AL2 and SPO256-AL2. Both devices are sold at the retail level by Radio Shack®. This chip-set is manufactured for the purpose of accepting input in the form of ASCII text strings and converting it to verbal output.

The intended purpose of this project is primarily experimental in nature. Instead of designing the device to serve a single purpose, maximum flexibility, as specified in the provided technical literature, is being sought. If successful, the completed unit will be limited in function only by the limitations designed into the components. This will allow the unit to be utilized in a variety of ways, depending on the software developed for it.

The finished unit should allow for data transmission through either a standard parallel port, or through a standard RS232 serial port. UART parameters for serial communications will be switch selectable.

A 2 kilobyte RAM buffer will be incorporated into the unit's design to lessen the demand of the unit on the computer's microprocessor time. This is desirable since speech is inherently much slower than normal microprocessor operations.

Finally, 4 kilobytes of EPROM space will be provided. This will allow for the storage of exception words, or words which will not be spoken properly otherwise. A good example of this is the author's last name, Hébert.

Upon completion, the author intends to use the unit primarily for reading the READ.ME documentation that often accompanies software. This can be accomplished with existing MS-DOS® utilities, therefore it is not intended to develop any specialized software to accompany this project.

## Research of Literature

### § THE NATURE OF SPEECH §

To understand the problems of generating synthetic speech, it is necessary to give a more detailed consideration of natural speech. Think of the numbers of people in our nation who are illiterate, despite being fluent in conversational English. Consider too that the Acadian French language, that variety of French indigenous to south Louisiana, had no written form until the mid 1970's. Noting these facts should make clear that a written language is an entirely different beast than its spoken counterpart.

In stark contrast to being identical to its spoken form, a written language is a mapping of one set onto another, not unlike what is done in the study of mathematics. Just as Des Cartes mapped algebra onto geometry by introducing the cartesian coordinate system, so has mankind mapped its spoken languages into a written form. Unfortunately or not, those governing the literary arts have not taken the same care to keep everything as well-defined as have the mathematicians. While this makes for some wonderfully moving literary works, and adds untold subtleties and nuances to the language, it also means there is no one-to-one correspondence between a written word and the sounds that comprise that same word in spoken form, (SPO256-AL2 Technical Data, 7).

Consider the character 'T'. It has one sound associated with it in the word 'teach', a different sound in the word 'bathe', and yet an entirely different sound in the word 'faction'. Conversely, there is no one-to-one correspondence between a given sound and the letter associated with it. As an example, consider the sound 'SH'. In the word 'shovel' it corresponds to the letters 'sh', but in the word 'faction' it corresponds to the letters 'ti'. If a one-to-one correspondence existed for transforming in either direction, it might be possible to define the transformation as a function and, at worse, have to deal with the elements of a preimage. Unfortunately, this is not the case.

Still, the mechanical transformation from text to speech can be accomplished. It is intuitive to anyone who can read this report that some words sound just like they look. Perhaps the foremost problem in generating synthetic speech is to document, in detail, every rule that determines just what constitutes sounding just like it looks.

But before that task can be done, it is necessary to decompose the spoken language into its fundamental components. Just as the written language has a finite number of components, (the twenty six characters of the alphabet and a handful of punctuation marks), so too has the spoken language. Those components are called phonemes. The English language is comprised of forty four phonemes, twenty five consonant phonemes and nineteen vowel phonemes, (SPO256-AL2 Technical Data, 8).

Everyone is familiar with the consonants and vowels of the written language. The letters 'a', 'e', 'i', 'o', 'u', and sometimes 'y' are the vowels, all others being consonants.<sup>3</sup> As was pointed out earlier, so too are the phonemes grouped. A phoneme is consonant if it is generated by an occlusion or obstruction of the breath channel, and it is a vowel phoneme if it is generated with an unobstructed or open breath channel, (SPO256-AL2 Technical Data, 8).

Each group of phonemes is further broken down into sub-groups. Vowel phonemes are classified as either high, mid, or low, and front, central, or back, depending on their general pitch and where they originate within the mouth. Table 1 shows each of the vowel phonemes as they are classified, (SPO256-AL2, 15).

| Vowel Phonemes | Front      | Central        | Back   |

|----------------|------------|----------------|--------|

| High           | YR, IY, IH |                | UW, UH |

| Mid            | EY, EH, XR | ER, AX         | OW, OY |

| Low            | AE         | AW, AY, AR, AA | AO, OR |

Table 1

The consonant phonemes are not so simply classified. First, the consonants are grouped by the point of occlusion which generates the sound.

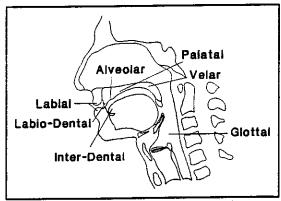

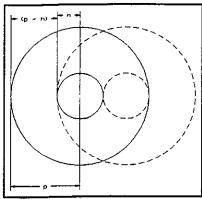

Those classifications are, (see figure 1), Labial, Labio-Dental, Inter-Dental, Alveolar, Palatal, Velar, and Glottal. Labial sounds are produced by bringing the lips together, either in or near contact. Labio-Dental sounds are the result of bringing the upper teeth in contact with the lower lip. Inter-Dental sounds occur when the tongue is placed between the teeth. Alveolar sounds are produced by touching, or nearly touching, the alveolar ridge with the tongue, (the

Figure 1: Points of occlusion for consonant phonemes.

<sup>&</sup>lt;sup>3</sup> As an aside note, though everyone knows that 'y' is sometimes a vowel, many do not realize the circumstances that make this so. The letter 'y' is a consonant if and only if it appears in the initial position of a word. If it appears in any position after the initial position, it is a vowel.

Also, it is apparently no longer taught that 'w' can be a vowel. One example of this is the word 'cwm', meaning a kind of valley forming a natural amphitheater. A more contemporary example would be the word 'vacuum', except in this case the letter 'w' has been decomposed into its original components, double 'u's.

alveolar ridge is just behind the upper teeth). Palatal sounds are the result of nearly touching the palate with the body of the tongue, as opposed to Velar sounds wherein the body of the tongue touches the velum, or the fleshy rear part of the roof of the mouth. Finally, Glottal sounds are produced by constricting the opening between the vocal cords, (SPO256-AL2 Technical Data, 14).

In addition to these classifications, consonant phonemes are also classified as either a Stop, a Fricative, an Affricate, a Nasal, or a Resonant. A Stop phoneme is one in which the sound abruptly terminates. A Fricative is generated by continually passing air through the associated occlusion. An Affricate is a combination of both a Stop and a Fricative, wherein the passing of air is terminated fairly quickly. Finally, Resonants and Nasals are both generated by reverberating a pitch in the breath channel. The difference is that Resonants are reverberated in the mouth, and Nasals are reverberated in the nasal cavity.

Lastly, each consonant phoneme is either voiced or voiceless. If the sound includes vibration of the vocal cords, it is voiced. If air is passed through the vocal cords without vibrating them, the phoneme is voiceless. Table 2 shows each of the consonant phonemes by classification, (SPO256-AL2 Technical Data, 14).

| T.         |                     | LABIAL   | LABIO-<br>DENTAL | INTER-<br>DENTAL | ALVEO-   | PALATAL       | VELAR    | GLOTTAL |

|------------|---------------------|----------|------------------|------------------|----------|---------------|----------|---------|

| STOPS      | VOICELESS<br>VOICED | PP<br>BB |                  |                  | TT<br>DD |               | KK<br>GG |         |

| FRICATIVES | VOICELESS<br>VOICED | WH       | FF<br>VV         | TH<br>DH         | SS<br>ZZ | SH<br>ZH      |          | нн      |

| AFFRICATES | VOICELESS<br>VOICED | ·-       |                  |                  |          | CH<br>JH      |          | ···     |

| NASALS     | VOICED              | мм       |                  |                  | NN       | <del></del> _ | NG       |         |

| RESONANTS  | VOICED              | ww       |                  |                  | RRLL     | YY            |          |         |

Table 2

Every word in the English language is spoken as some combination of the phonemes listed in tables 1 and 2. However, choosing the correct combination for a given word can be tricky at best. One phenomenon that is quickly discovered is that a given phoneme will sound acoustically different, depending upon its placement within a word, and within the context of those phonemes around it, (SPO256-AL2 Tech. Data, 8). This is due to the mechanics of the human anatomy generating the sounds. The result is that the synthetic generation of speech requires additional sound units, since

a machine will produce the same sound from the same phoneme every time regardless of placement or context.

### **§ THE SPO256-AL2 §**

To distinguish between the phoneme set which makes up a language and the set of sounds required to generate a language mechanically, the latter is called an allophone set. In the special case of the English language, an expanded set of fifty nine allophones is required. These are contained in the internal ROM of the SPO256-AL2. To simplify timing requirements in constructing words from allophones, the SPO256-AL2 also contains five pauses of various durations. This provides a total of sixty four allophone addresses.

| Decimal<br>Address | Hex<br>Address | Allophone | Sample<br>Word | Duration | Decimal Address | Hex<br>Address | Allophone     | Semple:  | Duration |

|--------------------|----------------|-----------|----------------|----------|-----------------|----------------|---------------|----------|----------|

| 0                  | 00             | PA1       | PAUSE          | 10 ms    | 32              | 20             | /AW/          | Out      | 370 ms   |

| 1                  | 01             | PA2       | PAUSE          | 30 ms    | 33              | 21             | /DD2/         | Do .     | 160 ma   |

| 2                  | 02             | PA3       | PAUSE          | 50 ms    | 34              | 22             | /GG3/         | Wig      | 140 ms   |

| 3                  | 03             | PA4       | PAUSE          | 100 ms   | 35              | 23             | /VV/          | Vest     | 190 ms   |

| 4                  | 04             | PA5       | PAUSE          | 200 ms   | 36              | 24             | /GG1/         | Got      | 80 ms    |

| \$                 | 05             | /OY/      | Boy            | 420 ms   | 37              | 25             | /SH/          | Ship     | 160 ma   |

| 6                  | 06             | /AY/      | Sky            | 260 ms   | 38 100          | 26             | /ZH/          | Azure    | 190 ma   |

| 7                  | 07             | /EH/      | End            | 70 ms    | 39:             | 27             | /RR2/         | Brain    | 120 ms   |

| 8                  | 08             | /KK3/     | Comb           | 120 ms   | 40              | 28             | /FP/          | Food     | 150 ma   |

| 9                  | 09             | /PP/      | Pow            | 210 ms   | 41              | 29             | /KK2/         | Sky      | 190 ma   |

| 10                 | 0A             | /JH/      | Dodge          | 140 ms   | 42              | 2A             | /KK1/         | Can't    | 160 ms   |

| 11                 | 0B             | /NN1/     | Thin           | 140 ms   | 43              | 2B             | 1 <b>22</b> 1 | Zoo      | 210 ma   |

| 12                 | 0C             | ЛHV       | Sit            | 70 ms    | 44              | 2C             | /NG/          | Anchor   | 220 ms   |

| 13                 | 0D             | /1772/    | To             | 140 ms   | 45.             | 2D             | /LIL/         | Lake     | 110 ms   |

| 14                 | 0E             | /RR1/     | Rural          | 170 ms   | 46***;;;        | 2E             | /ww/          | Wool     | 180 ms   |

| 15                 | 0F             | /AX/      | Succeed        | 70 ms    | 47              | 2F             | /XR/          | Repair   | 360 ms   |

| 16                 | 10             | /MM/      | Milk           | 180 ms   | 48:             | 30             | /WH/          | Whig     | 200 ms   |

| 17                 | 11             | /TT1/     | Part           | 100 ms   | 49:000          | 31             | /YY1/         | Yes      | 130 ms   |

| 18                 | 12             | /DH1/     | They           | 290 ms   | S0: 454         | 32             | /CH/          | Church   | 190 ms   |

| 19                 | 13             | /IY/      | Sec            | 250 ms   | S1::            | 33             | ÆR1/          | Fir      | 160 ms   |

| 20                 | 14             | /EY/      | Beige          | 280 ms   | 52.             | 34             | /ER2/         | Fir      | 300 ms   |

| 21                 | 15             | /DD1/     | Could          | 70 ms    | 53888           | 35             | /OW/          | Beau     | 240 ms   |

| 22                 | 16             | /UW1/     | To             | 100 ms   | 54000           | 36             | /DH2/         | They     | 240 ms   |

| 23                 | 17             | /AO/      | Aught          | 100 ms   | 55              | 37             | /SS/          | Vest     | 90 mas   |

| 24                 | 18             | /AA/      | Hot            | 100 ms   | 56              | 38             | /NN2/         | No       | 190 ms   |

| 25                 | 19             | /YY2/     | Yes            | 180 ms   | 57:             | 39             | /HH2/         | Ное      | 180 ms   |

| 26                 | 1A             | /AE/      | Hat            | 120 ms   | 58. **          | - 3A           | /OR/          | Store    | 330 ms   |

| 27                 | 1B             | /HH1/     | He             | 130 ms   | 59              | 3B             | /AR/          | Aiarm    | 290 ms   |

| 28                 | 1C             | /BB1/     | Business       | 80 ms    | .60             | 3C             | /YR/          | Clear    | 350 ms   |

| 29:                | 1D             | /TH/      | Thin           | 180 ms   | ól              | 3D             | /GG2/         | Guest    | 40 ms    |

| 30                 | 1E             | /UH/      | Book           | 100 ms   | 62              | 3E             | ÆL/           | Saddle   | 190 ms   |

| 31                 | 1F             | /UW2/     | Food           | 260 ms   | 63::            | 3F             | /BB2/         | Business | 50 ms    |

Table 3

Table 3 lists all 64 allophones contained in the speech chip, (SPO256-AL2 Technical Data, 18). Constructing a vocal tract, (a spoken word or phrase), is simply a matter of addressing the appropriate allophones in the proper sequence. Since speech is significantly slower than normal microprocessor operations, each allophone can be output, (or *spoken*), as it is addressed. Terminating a word requires the addressing of a pause of appropriate length. Failure to address pauses between words will result in a phrase being spoken as a single word.

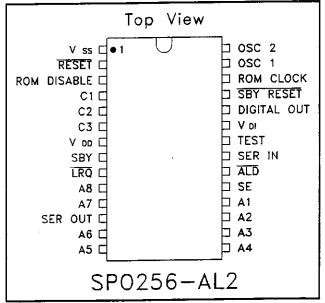

Two modes are available for addressing allophones in the SPO256-AL2. The addressing mode is selectable by pin 19, Strobe Enable, (SE).

Mode 0, (SE = 0), latches an address when any address pin(s),  $(A_1 - A_8)^4$ , make(s) a positive transition. There are two disadvantages to using this mode. First, timing is critical since latching occurs on the PGT edge of any one of the address lines. The second disadvantage is that PA1, the 10 ms pause, cannot be loaded.

Mode 1, (SE = 1), latches whatever address is setup on the address lines at the

Figure 2: Pinouts of the SPO256-AL2

NGT edge of pin 20, ALD, (Address Load). Timing requirements are less critical in mode 1. The ALD pulse time should be no less than 200 ns, and no greater than 1100 ns. Address line transitions should occur no less than 80 ns before the ALD pulse, and should hold for at least 80 ns after the ALD pulse, (SPO256-AL2 Technical Data, 4).

Two pins are available for interfacing the SPO256-AL2 to a microprocessor. They are Load Request, (LRQ, pin 9), and Standby, (SBY, pin 8). LRQ is an active low pin. LRQ remains high during allophone output operations, and returns low upon completion indicating the appropriate time to load the next address. SBY is also active low. SBY assumes a logical high state until an address is loaded and goes low during allophone output processing.

<sup>&</sup>lt;sup>4</sup> The documentation accompanying the SPO256-AL2 specifies the address pins as  $A_1 - A_8$ . The author does not know why the manufacturer did not use the accepted standard exponential  $A_0 - A_7$  notation. In any case, to avoid confusion between this report and the manufacturers data sheets, the same notation is used here.

Even though both pins are active low by definition, they operate inversely in that LRQ provides a logical low signal at the appropriate time for a new address and SBY provides a logical high. Either pin may be used depending on the signal level required.

When an address is loaded, the allophone associated with that address is output serially over pin 24, (Digital Out), as a digital bit pattern. This digital sequence can then be channeled through a low pass filter. Since the digital signal is a square wave, and a square wave can be defined as a sum of odd harmonics, (the well known Fourier series):

$$f(x) = \frac{2}{\pi} \sum_{n=1}^{\infty} \frac{[1 - (-1)^n]}{n} Sin(nx)$$

filtering out the higher harmonics, (n » 1), will decompose the square wave into a sinusoidal waveform. That sinusoidal waveform can then be amplified as an audio signal and output over a speaker.

### § THE CTS256A-AL2 §

Though the spoken language has been subdivided into fundamental components, and those components have been encoded into a specialized microprocessor, it remains to address them appropriately to construct meaningful vocal tracts. Toward that end, Naval Research Laboratories developed an algorithm to convert text strings into an appropriate string of allophone addresses. That algorithm is the basis for the op-code contained in the CTS256A-AL2, (CTS256A-AL2 Technical Data, 7).

The CTS256A-AL2 is actually a General Instruments® PIC7041 8-bit microprocessor, (a licensed second source of the Texas Instrument® TMS7041). The PIC7041 has 4 kilobytes of internal ROM, and 128 bytes of internal RAM. In the CTS256A-AL2, the internal ROM has been masked with op-code which enables it to convert ASCII text strings into allophone addresses compatible with the SPO256-AL2. The internal op-code also allows the user to run additional op-code stored in external ROM, but with somewhat less flexibility than the standard PIC7041.

The PIC7041 has four memory expansion modes available to the user. They are single chip, peripheral, full, and microprocessor expansion modes. The op-code masked into the CTS256A-AL2 sets the chip to the full expansion mode upon power up. This allows the 128 bytes of internal RAM

and the 4 kilobytes of internal ROM to be utilized, and it allows for external addresses from 0200H to EFFFH, (Microchip® DS33001A, 15). Additionally, the built-in op-code allows for the following optional configuration features, (CTS256A-AL2 Technical Data, various pages).

#### ¶ EXTERNAL ROM ¶

The CTS256A-AL2 allows for external ROM which can be used to store either exception words, (words which would not be pronounced properly), or user op-code. There is no default address for the external ROM, but its beginning address, (X000H), must fall on a 4K boundary such that 1000H

X000H

E000H. The existence of external ROM is specified by the five byte sequence 80H 48H 28H 58H 85H located at addresses X000H - X004H. Additionally, other segments of external ROM are reserved for special op-code to set it up as either an exception word ROM bank, or a user code ROM bank. Further discussion of the use of External ROM can be found in the chapter entitled Testing and Results, paragraph heading External ROM, (General Instrument® Product Data, 78).

#### ¶ EXTERNAL RAM ¶

An external RAM buffer can be added to the CTS256A-AL2. RAM must be added in 256 byte blocks, it must be contiguous, and a minimum of 512 bytes is required. External RAM must have an access time not greater than 250 ns. The default address of the external RAM buffer is 3000H and is redefinable in external ROM, (General Instrument® Product Data, 78).

#### ¶ PARALLEL DATA PORT ¶

The CTS256A-AL2 contains a built in UART, (Universal Asynchronous Receiver Transmitter), which can accept data, or it can accept data via a parallel port. The default address for the parallel port is 0200H, but is redefinable in external ROM, (General Instrument® Product Data, 79).

<sup>&</sup>lt;sup>5</sup> The reference material listed as General Instrument Product Data is actually a section of a reference book provided by Tandy, Inc. Since only those pages pertaining to the CTS256A-AL2 were provided, (pp 77 - 95), the actual title of the book is unknown.

### ¶ SWITCH SELECTABLE UART PARAMETERS ¶

By default, the CTS256A-AL2 will use UART parameters of asynchronous communication, 7 data bits, 2 stop bits, and no parity. Switch selected parameters can be specified via a 74LS373 buffer. The default address of this buffer is 1000H, and is redefinable in external ROM, (General Instrument® Product Data, 80).

#### ¶ PINOUT INFORMATION ¶

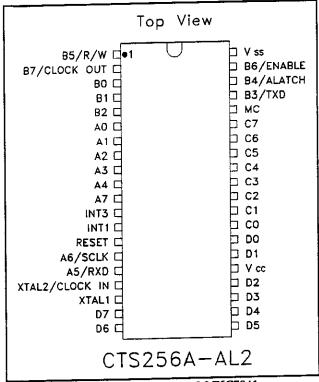

Figure 3 shows the pinouts of the CTS256A-AL2. In this section, the pin functions will be described as they pertain to the PIC7041. These descriptions will then be qualified to relate their operation within the context of the CTS256A-AL2.

Pin 36, (MC, Mode Control or Memory Control), is an input pin which is used to specify the operation, (or memory expansion), mode of the PIC7041. If MC is held at logical hi it will force the microprocessor into the microprocessor expansion mode of operation, disabling the microprocessor's ability to access either the internal RAM or ROM and forcing all 64K addresses to be external. Holding MC at logical lo allows internal address space to be accessed,

Figure 3: Pinouts of the CTS256A-AL2/PIC7041

and the expansion mode is set by software, (General Instrument® DS33001A, 16). Since the op-code contained in the CTS256A-AL2 requires full expansion mode, MC must be held at logic level 0.

Of the microprocessor's 40 pins, 32 are I/O ports labeled  $A_0$  -  $A_7$ ,  $B_0$  -  $B_7$ ,  $C_0$  -  $C_7$ , and  $D_0$  -  $D_7$ , (ports A, B, C, and D).

Port A lines  $A_0$  -  $A_4$  and  $A_7$  are bi-directional lines, and  $A_5$  -  $A_6$  are input only, (General Instrument® DS33001A, 16). In the case of the CTS256A-AL2, lines  $A_0$  -  $A_4$  and  $A_7$  are used to specify configuration parameters, (see table 4 on the next page). Line  $A_5$  is RXD, (Receive Data), for the built-in UART, and line  $A_6$  is not used.

Port B is an output only port, and is utilized as follows in the CTS256A-AL2. Line  $B_0$  is used for handshaking purposes for both the serial and parallel port. When the input data buffer, (internal or external RAM), reaches 86.5% full,  $B_0$  goes to logic level 0. When the buffer's contents are reduced to 50%,  $B_0$  returns to logic level hi, (CTS256A-AL2 Technical Data, 2). Lines  $B_1$  -  $B_3$  and  $B_7$  are not used, though  $B_3$  is the TXD, (Transmit Data), for the built-in UART. Line  $B_4$  is used as an address latch control line when port C is used to output the least significant byte of an address. Line  $B_5$  is used as read/write control for external RAM, and line  $B_6$  is used to enable the chip-select device, 74LS138.

| Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 (A <sub>0</sub> )  | 7 (A <sub>1</sub> ) | 8 (A <sub>2</sub> ) | Mode                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|---------------------|--------------------------------------------------------------------------------------|

| silven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                    | 0                   | 0                   | Parallel Port Input                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                    | 0                   | 1                   | Serial Port Input; 50 Baud                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                    | 1                   | 0                   | Serial Port Input; 110 Baud                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                    | 1                   | 1                   | Serial Port Input; 300 Baud                                                          |

| i de la composición dela composición de la composición dela composición de la composición de la composición de la composición dela composición de la composición de la composición dela composición de la composición de la composición de la composic | 1                    | 0                   | 0                   | Serial Port Input; 1200 Baud                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                    | 0                   | 1                   | Serial Port Input; 2400 Baud                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                    | 1 .                 | 0                   | Serial Port Input; 4800 Baud                                                         |

| 95<br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                    | 1                   | 1                   | Serial Port Input; 9600 Baud                                                         |

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9 (A <sub>3</sub> )  |                     |                     | Mode                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0<br>1               |                     |                     | Default UART Parameters: Asynchronous, 7, 2, None<br>Switch Selected Uart Parameters |

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 (A <sub>4</sub> ) |                     |                     | Mode                                                                                 |